IMEC has transferred its Copper-Top (Cu-top) interconnect process technology to National Semiconductor’s production facility in Malacca, Malaysia. The Cu-top technology is a low resistance, post-passivation interconnect module particularly suited for analog and mixed-signal applications. It improves system-efficiency and results in a significant chip-size reduction of such semiconductor devices.

The Cu-top module can be added to any semiconductor product wafer for current carrying capability. The sheet resistance of the interconnect layer is much lower than today’s standard back-end aluminum (Al) interconnects, therefore, making the technology especially suited for analog and mixed-signal applications where relatively large electrical currents are used. The technology overcomes the resistive voltage drop and power-loss caused by the low conductivity of traditional interconnects resulting in a significant increase of the system efficiency. It prevents the use of wide metal lines and hence reduces chip areas.

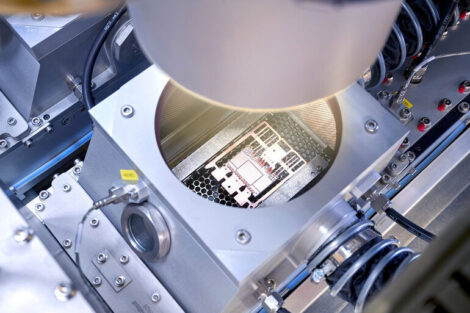

The key feature of this technology is the use of Cu plating in a photoresist pattern, allowing for a small line width to enable a high-density high-current interconnect layer. The contacts through the 2 µm thick IC passivation have a diameter of only 3 µm and have a very good contact resistance between the plated Cu and the underlying Al layer. The Cu layer on the chip is protected by a 10 µm thick polymer dielectric layer. This layer is photo-defined to clear scribe lanes and bonding pads. The Cu bonding pads are covered with an Al metallization to allow for testing and wire-bond packaging.

The process development and technology transfer results from a three-year close collaboration between IMEC’s thin-film technology group and a team from National Semiconductor Santa Clara, California (USA) and Malacca.

EPP Europe 468

Share: