It goes almost without saying: the ever increasing pressures to reduce cost, increase quality and shorten time to market is an unending task in electronics manufacturing. Test strategies can provide advantages by improving the efficiency and quality of processes, and by driving cost reductions and improved performance through the entire product lifecycle from design, through product introduction, manufacturing and warranty. The return-on-investment of an optimized board test strategy can total three weeks improved time-to-market, and over one million euro. Here we´ll just begin with the bottom line: what is driving those pressures and what can remedy them?

Manufacturers need to deploy complementary and distributed test strategies, using the strengths of various testers to achieve a greater combined performance. Engineers have often used experience as a means for assigning test strategies without analyzing the benefits and weaknesses of different test approaches in a quantitative manner. But complex boards require a more optimized strategy. GR Force/Strategist from Teradyne is a software tool that helps to design and implement optimized test plans by modeling the fault coverage (effectiveness of a test method detecting a specific defect type on a location that is fully accessible) of each individual test stage on component-pin level. This tool enables testability analysis during board design, and enables test engineers to work concurrently with designers.

This type of complex analysis can only be performed with software that takes advantage of the complete geometrical, electrical and mechanical board design information that lies within formats like GENCAM. (This format, IPC standard 2541, establishes requirements and other considerations for the interchange of information between software and factory information systems.) The benefits of using Strategist are fewer design iterations, better test access, improved fault coverage, fewer snags, lower production test costs and improved time-to-market. Different factors constrain test strategies on boards that serve different requirements. Access, cost, throughput, reliability, test development time and diagnostic resolution are all relevant and important factors in determining an optimized test plan. Strategist enables engineers to balance these tradeoffs and make decisions that best meet their objectives. It helps engineers decide what equipment should be part of the tests and then assists them in implementing the strategy on the shop floor by automatically generating the input files required by the equipment. By providing the flexibility to create synergistic test strategies with equipment from multiple vendors, the tool makes more agile in solving tough problems.

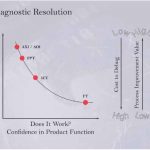

Manufacturers have a multitude of issues to consider when designing test strategies for board assemblies, including automated optical (AOI) and X-ray inspection (AXI), flying-probe (FPT), functional (FT) and in-circuit test (ICT) as well as boundary scan (BS). Each of these has its own fault coverage and performance characteristics. Engineers must balance tradeoffs between operating and capital costs, fault coverage, throughput, diagnostic resolution, immediacy of process feedback and long-term product reliability when considering an optimal test strategy. The loss of physical test access adds another dimension of complexity to the problem; determining fault coverage and prioritizing the nets that require physical access in a boundary-scan and digital-test environment is a difficult challenge. By using multiple test techniques in a complementary or distributed manner, users can best achieve their goals.

A wealth of questions has to be resolved. Which tools are to be use in a distributed test strategy? What is the fault coverage provided by each technique? How should tests be distributed to achieve performance goals? What is the correct balance of complementary vs. overlapping test coverage? Which nodes require test access and which do not? What are the risks/gaps in an optimized strategy? Users are trying to answer these questions, and, furthermore, increasing time-to-market pressures mandate that strategies have to be optimized early during the design stage.

Complementary and distributed test strategies

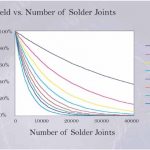

The trend toward increased product complexity and miniaturization results in increased I/O and board density. Consequently, we can find boards with solder joint counts that exceed 20,000. Concurrently, assembly process complexity is also increasing; boards often undergo double sided SMT assembly, manual assembly, wavesoldering, press-fit and mechanical assembly stages. Even though manufacturers are improving their process capabilities and reduce defect rates, they are finding it difficult to keep the number of defects per board on a declining trend. The increasing number of solder joints per board combined with increased complexity is leading to a higher number of structural defects. Structural faults are defined as those that are soldering, placement, assembly and mechanical in nature including shorts, opens, poor solder fillet quality, solder voids, wrong and skewed and missing components. Structural faults do not include those defects that are electrical in nature, as a result of design and incorrect value or non-functional parts. A study on a worldwide basis measured structural defect rates averaging 650 to 1100ppm (defective solder joints per million joints produced). Figure 1 shows that even a manufacturer who attains ”world class” quality levels of 100ppm structural defect rate are guaranteed (near) single digit yields when 20,000 solder joints are present.

As first-pass yield approaches the single digits, manufacturers have to pay more attention to the structural fault spectrum, which typically accounts for 80 to 90% of all flaws. This trend is causing engineers to consider automated inspection that is capable of detecting structural failures earlier in the manufacturing process as part of a broader test strategy. Also, the density and complexity of board assemblies is rendering long used human visual inspection methods ineffective, and the increased component density is reducing the level of physical access available for bed-of-nails testing (ICT). This reduced access translates into reduced electrical test coverage, thereby drivingthe adoption of non-contact methodologies as AOI, AXI and FPT to provide complementary test coverage.

Time-to-market pressure

As product life cycles approach in the order of one year, time-to-market is a key focus area. The faster organizations move from design to prototype to production, the higher their market-share, revenues and profits. A software tool that enables testability analysis during board design would improve time-to-market because it would enable test engineers to work concurrently with designers. When engineers can predict the fault spectrum, plan test strategies, understand fault coverage and test access tradeoffs before the PCB layout routing stage, they can achieve significant competitive advantage. The bottom line is fewer design iterations, fewer snags, lower test costs, improved manufacturing efficiencies and improved time-to-market.

In addition to software tools that enable testability analysis during board design, users are looking for alternative strategies that reduce test development time and facilitate a fast yet effective NPI cycle by providing a high level of fault coverage and diagnostic resolution at such an early product stage. Fixture-less methods like FPT that exhibit high levels of fault coverage and fast test development without the requirement for expensive and long delivery-time fixtures are highly desirable for NPI.

Time-to-volume pressure

Companies satisfying demand for innovative products early in their life cycle can win both market share and profits. Ramping production volumes in a cost-competitive environment requires effective detection and containment of defects at source, root cause identification and ultimately better process capability. Inspection methods such as AXI/AOI that provide parametric data for process measurement, continuous improvement and control will help to deliver better yields over time. Users need test solutions that find defects closer to source with excellent diagnostic resolution for immediate rework. High levels of diagnostic resolution minimize WIP (work-in-process) and RIP (repair-in-process), ensure fast debug and repair, and facilitate short product cycle times and high-volume manufacturing. Time-in-process can be substantially reduced by using test strategies that include automated inspection techniques to complement electrical ICT and functional test (FT) methods.

The benefits of these combined strategies are manifold. Because of earlier prototype testing, a faster time-to-market is possible. Close to 95% of test coverage of structural defects can be achieved within hours of application development, as opposed to days for an ICT test approach. A very high quality can be attained of boards shipped, because structural defects are found at automated inspection that would not be detected by electrical methods. If not found, such structural defects can lead to latent defects, reduced product reliability, field returns and increased warranty costs. Also to expect are reduced costs at ICT/FT and environmental stress screening (ESS) through reduced debug and repair. By distributing the test task to the most appropriate resource, fault coverage can be maximized at the earlier stages where diagnosis and rework can be completed at much lower cost. Shorter product cycle times and improved asset utilization are possible through reduced retest-debug-rework loops at ICT/FT and ESS. For high-complexity boards, a distributed test approach can shorten the overall time-in-process by a factor of three through reduced time in debug and repair. (A high complexity board is defined as with more than 3,000 nodes or 15,000 solder joints, respectively, destined for a high-reliability application similar to workstation computing or telecom switching – not a disposable consumer product. Such electronics is at least IPC Class 2.) Therefore, a distributed test approach can dramatically improve asset utilization and inventory turns.

This three-fold series on board test and inspection technologies has been or will be presented in the issues #11/12 and the following editions in 2003 of EPP Europe. The overview is based on information provided by Teradyne Assembly Test group, and derives primarily from a paper of AXI and test strategy expert Amit Verma.

Short board test glossery

Distributed test – a strategy that leverages the strengths of various test machines (measured by fault coverage, access, test speed, diagnostic resolution or other attributes) in both complementary and overlapping manners to achieve a combined performance that is equal to or greater than the sum of the individual methods.

Fault spectrum – the defect type possibilities and the locations where they may occur on a PCBA.

Fault coverage – the effectiveness of a test stage at detecting a specific defect type on a location that is fully accessible.

GENCAM – this data format complies with IPC standard 2541, and establishes requirements and other considerations for the interchange of in-formation between manufacturing software and factory systems. Information may consist of at-tribute and parametric data, product data, pro-cess recipes, equipment monitoring and control, resource utilization and material consumption (www.gencam.org)

Test access – the level of access that a test stage has to the PCBA. For example, ICT can have less than 100% access to the signals, while 2D/AXIcan have less than 100% access to the solder joints. The concept of test access is independent of fault coverage.

Test coverage – the product of fault coverage x test access

Testability analysis – all available CAD and BOM information are used to determine ICT physical access. The fault coverage of other test methods like AXI, FPT or AOI are factored into the model, and tradeoffs are made as to which test should provide coverage on which parts and pins. Any lack ofaccess is investigated and test pad requirements are determined based on the fault coverage of all test stages, and the model library information (BS, analog, digital).

Important acronyms and abbreviations

AOI automated optical inspection

API automated paste inspection

AXI automated X-ray inspection

BIST built-in self test

BS boundary scan´/IEEE 11.49.1

BOM bill of material

CAD computer aided design

CEM contract electronics manufacturing/manufacturer

DFM design for manufacturing

DFT design for test

DFx design for test & manufacturing

ESS environmental stress screening

ICT in-circuit test

FPT flying-probe test

FT functional test

HVI human visual inspection

MDA manufacturing defect analyzer

NPI new product introduction

OEM original equipment manufacturer

PCB printed circuit board

PCBA printed circuit board assembly

QFP quad flat pack

RIP repair/rework in process

ROI return on investment

SMT surface mount technology

TAP test access port [boundary scan]

WIP work in process

ZUSAMMENFASSUNG

In dieser dreiteiligen Serie (publiziert in den Ausgaben 11/12, 1/2, und 3/4 von EPP Europe) steht die Organisation von Teststrategien in der Baugruppenfertigung im Mittelpunkt. Dabei geht es nicht nur um den erstrebenswert frühen Datenaustausch zwischen Design und Fertigungsprüfung in der Produktdefinitionsphase für Concurrent Engineering, sondern auch um das später relevante Test-Konzept im Prüffeld, das sich im Bedarfsfall auf alle verfügbaren Verifikationsmethoden stützt. Der Vorteil richtig gewählter Prüfstrategien: Kosten können weiter gesenkt und die Qualität sowie Zuverlässigkeit der Baugruppen besser verifiziert werden.

RÉSUMÉ

Cette série de trois articles (publiés dans les numéros 11/12, 1/2 et 3/4 de EPP Europe) est consacrée à l’organisation des stratégies de test dans la fabrication de sous-groupes. Il n’est pas uniquement question de l’échange de données que l’on souhaite le plus précoce possible entre la conception et le contrôle de production dans la phase de définition du produit pour le Concurrent Engineering, mais également du concept de test ultérieur, au banc d’essais, qui fait appel, si nécessaire, à toutes les méthodes de vérification disponibles. L’avantage des stratégies de test bien choisies réside dans la possibilité de réduire davantage les coûts et de mieux vérifier la qualité et la fiabilité des sous-groupes.

SOMMARIO

In questa serie da tre componenti (pubblicata nelle edizioni 11/12, 1/2, 3/4 della EPP Europe) l’organizzazione delle strategie di test all’interno della produzione di gruppi costruttivi si trova al centro dell’attenzione. Qui non si tratta solo di uno scambio di dati precoce auspicabile tra design e controllo di produzione nella fase definitiva dei prodotti per la Concurrent Engineering, bensì anche del concetto di test rilevante in un secondo momento nel campo di controllo che, all’occorrenza, si basa su tutti i metodi di verifica. Il vantaggio di strategie di controllo correttamente scelte: i costi possono essere abbassati ulteriormente e la qualità nonché l’affidabilità dei gruppi costruttivi possono essere verificate molto meglio.

Share: